DRY ETCHING OF CONTACT WINDOWS IN SILICON DIOXIDE USING CHF3

Patrick Verdonck\*, Fedor Coopmans and Gilbert Decleck, ESAT laboratory, KULeuven, Kar dinaal Mercierlaan 94; B 3030 Heverlee, Belgium

Due to decreasing in LSI, VLSI, (ULSI), dry etching steps (Plasma etch, RIE, RIBM...)replace most wet etchings. Initially, most of the attention was paid to patterning of silicon nitride and polysilicon (etching steep walls with no undercut. Only during the last 2 years, dry etching of silicon dioxide became a hot topic. This paper gives a description of an integrated process for etching contact windows in silicon dioxide. Also basic mechanisms of the silicon dioxide etching are explained.

Integrated Circuits,Dry etching

# I. INTRODUCTION

After etching the contact windows, an aluminium layer is deposited. After etching and sintering, this layer must make a good contact with the underlying polysilicon or monosilicon. However, very often the contact is made upon a shallow junction (0.1-0.2 um), with high dopant concentration. No contact must be made with the bulk, under the junctions! Thus not much of the monosilicon of these junctions may be removed. An extra difficulty is the relatively bad uniformity of a deposited silicon dioxide layer. While silicon nitride, polysilicon and aluminium layers are deposited very uniformly, even state of the art silicon dioxide equipment yields an uniformity of  $\pm$  5%. This means a difference of 100 nm over a 1 um thick isolation film. Thus a (very) selective process is needed.

Furthermore, the aluminium layer must not crack on the edge of the contact hole. Therefore, using wet etching, reflow of a PSG- oxide was necessary. However, if the holes can  $\operatorname{im}$  mediately be etched with sloped walls, no reflow step is needed anymore, resulting in shorter production times.

<sup>\*</sup> Patrick Verdonck is actually with the CTI/SEI, Instituto de Microeletrônica, Caixa Postal 6162, 13100 Campinas, SP, Brasil

## II. SELECTIVITY: EXPERIMENTAL:

A parallel plate batch system, with a 13.56 MHz RF-generator is used. Gas flow, pressure, temperature and power can be controlled independently. Both electrodes can be powered.

Free fluorine etches silicon much faster than silicon dioxide. In the ESAT -laboratory, a selectivity of over 30:1 is obtained in the polysylicon process. Selectivity between silicon dioxide and silicon can be obtained free fluorine with hydrogen and forming a polymer layer of chemical composition: CXFy on the silicon surface.

Various parameter changes were observed. Some of them, adding nitrogen for instance did not affect selectivity. Temperature has to be kept at about 20°C to avoid uncontrolled resist erosion. Increasing power results in a linear increase of the oxide etchrate and the silicon etch rate, nearly without affecting selectivity. However a lower limit of about 500 W was found, where no more oxide etching occured, because of poor bombardment, and also an upper limit of about 2300W, where resist erosion became a serious problem. For production a relatively high power will be used, because of throughput considerations.

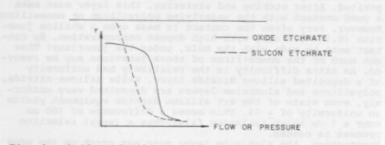

The influence of CHF  $_3-$  flow and pressure are impressive.Etch rates decrease with increasing flow, pressure as indicated in fig. 1

Fig. 1 - Oxide and Silicon etchrate in function of flow or pressure.

The absolute values of flow, pressure and etch rates depend on, amongst others, power, temperature and also on wafer diameter. For a 2 inch wafer a process with selectivity 40:1 was developed. However, etching a 3 inch wafer with this process was found impossible. To obtain a 30:1 selective

process, flow was held constant and pressure decreased.Because of reproductibility problems, a 20:1 selective process is used in production. Most commercial etchers use processes with selectivities of 15:1 or less.

# 3. SELECTIVITY: DISCUSSIONS:

To understand the results as seen in fig. 1, some-oversimpli-fied- chemical reactions have to be taken into account.

Reactions in the plasma:

$$CHF_{3} - CF_{3}^{+} + H + e - (1)$$

$CHF_{3} - CHF_{2} + F$  (2)

$H + F - HF$  (3)

Reactions on the oxide surface:

$$SiO_2 + 4F \longrightarrow SiF4 + O2$$

(4)

$CxFy + O2 \longrightarrow Cx-1Fy + CO2$ (5)

$CxFy + O2 \longrightarrow Cx-2Fy + 2CO$ (6)

The higher the C/F ratio in a plasma, the more polymerization is favoured over etching. The role of the Hydrogen atom in the CHF, module is to scavenge free fluorine (reaction 3) The HF does not react and is removed. Hence the C/F ratio increases, just as polymerization. In a certain flow and pressure range, the oxide etch rate is considerably higher than the silicon etch rate. The CxFy polymer is formed as well on the top of the silicon as on the top of silicon dioxide. On the silicon surface the polymer grows thicker and thicker in these flow and pressure range. However the free oxigen that is obtained in reaction (4) can serve as an etch reactant with the polymer as seen in reactions (5) and (6). Thus on the top of the oxide layer the polymer is removed and etching continues. Increasing flow and /or pressure, more polymer is formed, in this way decreasing the etch rate. At a certain point too much polymer is formed on the top of the silicon dioxide, so that bombardment will be insufficient to etch more silicon dioxide, resulting in a sudden drop in the etch rate curve of fig.1; (bombardment also decreases with increasing pressure, enhancing this effect!) Because the bull's eye effect (i.e. higher etch rate at the side than at the centre of the water) on a 3 inch wafer is more important than on a 2 inch wafer, the oxide in the centre of a 3 inch wafer is more difficult to remove. As selectivity we defined the smallest etch rate of the oxide (in the centre), divided by the highest etch rate of the silicon, at the side of the wafer. At the centre of the silicon wafer, so little silicon is removed, that it is impossible to measure it, often there is even no visible profile.

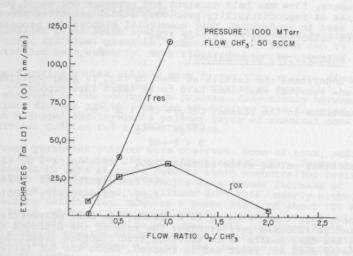

Fig. 2 - Oxide etchrate (rox) and resist erosionrate (r<sub>res</sub>) in function of oxygen dilution.

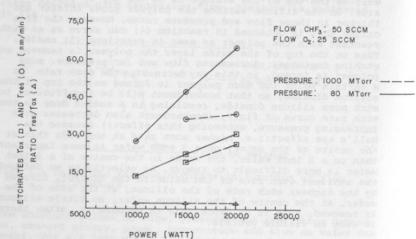

Fig. 3 - Oxide etchrate (rox) and resist erosionrate (r res)

#### 4. TAPERED WALLS: EXPERIMENTAL

Isotropic etching of silicon dioxide is impossible in our equipment: Controlling resist erosion, reproducable tapered walls can be obtained. With Microposit 1350H resist and with standard postbake a 2:1 resist erosion rate to oxide etch rate was experimentally determined to obtain 459 tapered walls.

Oxygen dilution is a very important parameter, as can be seen in fig.2. Fig. 3 shows that the huge changes of pressure and power influence the etch and erosion rate but that they almost do not affect the ratio (+ 10%). Changing the resist threatment, especially the postbake step, influences the resist erosion more than could be imagined. Still, in production all oxide walls have a slope between 45% and 55% also depending on linewidht. Step coverage of 2 micron wide aluminium lines over 100 steps has a yield of over 99% (when the process described below was used).

#### 5. TAPERED WALLS: DISCUSSION

At low oxygen dilutions, the oxide etch rate increases with increasing oxygen flow. Hydrogen tends to form  $\rm H_2O$  rather than HF. Much less free fluorine will be scavenged. Furthermore, the oxygen will also form CO and CO\_, so the C/F carge will decrease so much that nearly no polymer is formed anymore. This has of course also its influence on the silicon etch rate:for dilutions 1 (O\_): 2 (CHF\_3), the silicon etch rate is 5 X the oxide etch rate. With oxygen flow higher the CHF\_3 flow, the oxide etch rate decreases due to lack of active species.

The erosion etch rate increases linearly with increasing dilution, even till a 2:1 dilution. Erosion is a chemical etching: Chemical reaction of the photoresist with the oxygen(at 1000 mtorr pressure).

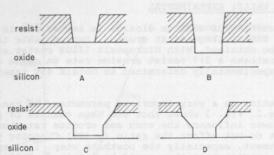

## A THREE STEP PROCESS (fig. 4)

It is impossible to etch a 1 um thick oxide layer with a slope of 459, when a 1.5 um thick resist with a 809 slope is used (decreasing the angle yields less packing density). Thus the first step has to be an anisotropic, very uniform, fast etching, which removes about 0.5 um oxide, without damaging resist. The second step is the resist eroding etching, which removes also about 0.5 um. The third step is the selective etching. Afterwards an oxygen dry strip step is used to remove the remaining photoresist and the polymer on the top of the silicon substrate.

Fig. 4 - Profiles of the contact windows and resist.

- a) before etching

b) after the first step

c) after the second step

- after the third step (process completed).

#### CONCLUSIONS

Silicon dioxide, silicon and photoresist etchings are studied as function of gases, flows, pressure, power and temperature. To obtain a selective oxide to silicon etch process, CHF2 gas flow and pressure have to be chosen carefully whithin a dertain range. To obtain controlled tapered walls the oxygen dilution has to be determined for each resist and for each process. The other parameters may vary within large ranges. A 3 step integrated process has been proposed that etches contact windows in silicon dioxide with tapered walls, which results in excellent aluminium step coverage, and with nearly no attack of the underlying poly and monosilicon.

#### ACKNOWLEDGEMENTS:

The authors wish to thank Guy Brasseur, Emiel Niclaes and the silicon process group of the ESAT laboratory for their support and interest.